锐杰微科技携晶上系统破局算力瓶颈,首发3DIS™平台引领先进封装创新

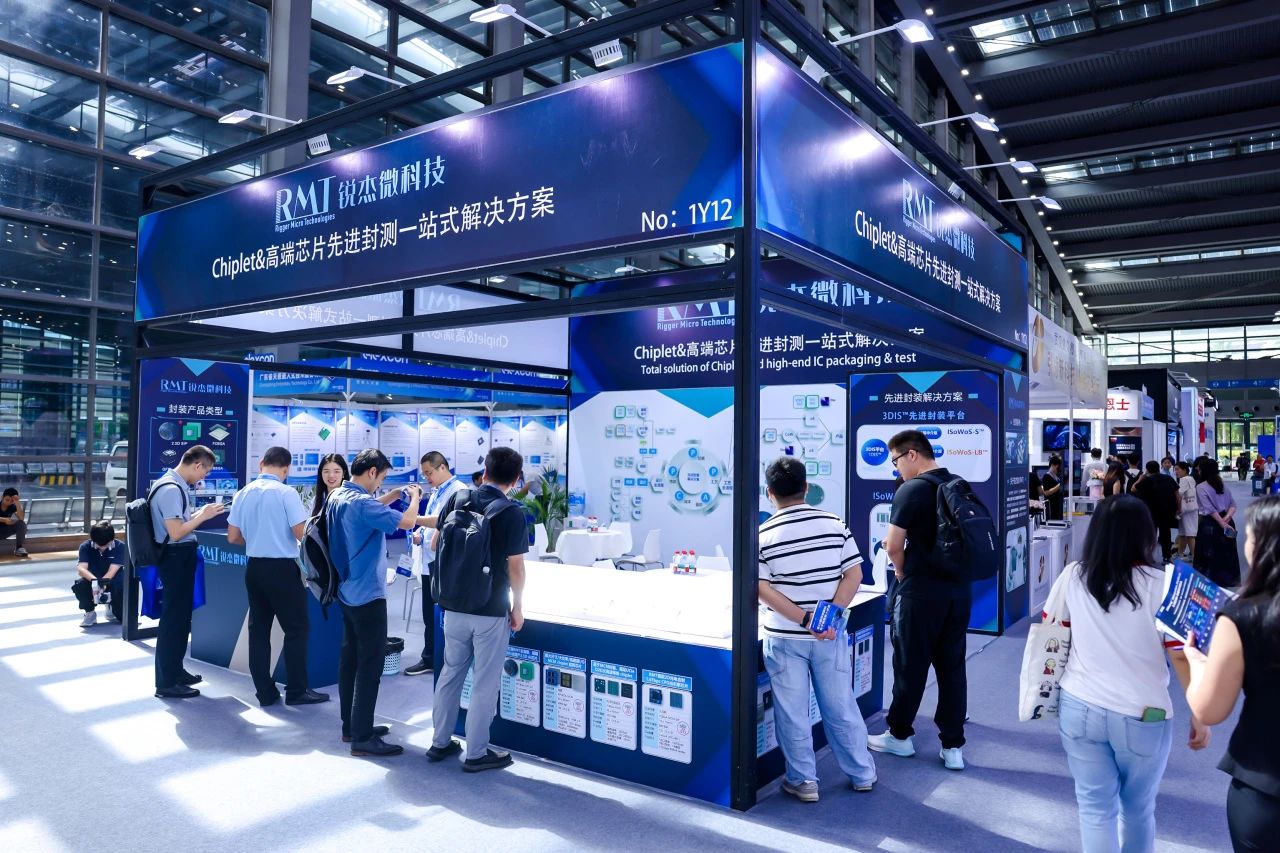

8月26日-28日,第九届中国系统级封装大会在深圳(福田)会展中心盛大举行。作为Chiplet&高端芯片设计和工艺全流程的封测制造方案商,锐杰微科技在本次展会上精彩亮相,首发3DIS™先进封装平台,全方位展示了其领先的技术实力与创新成果。

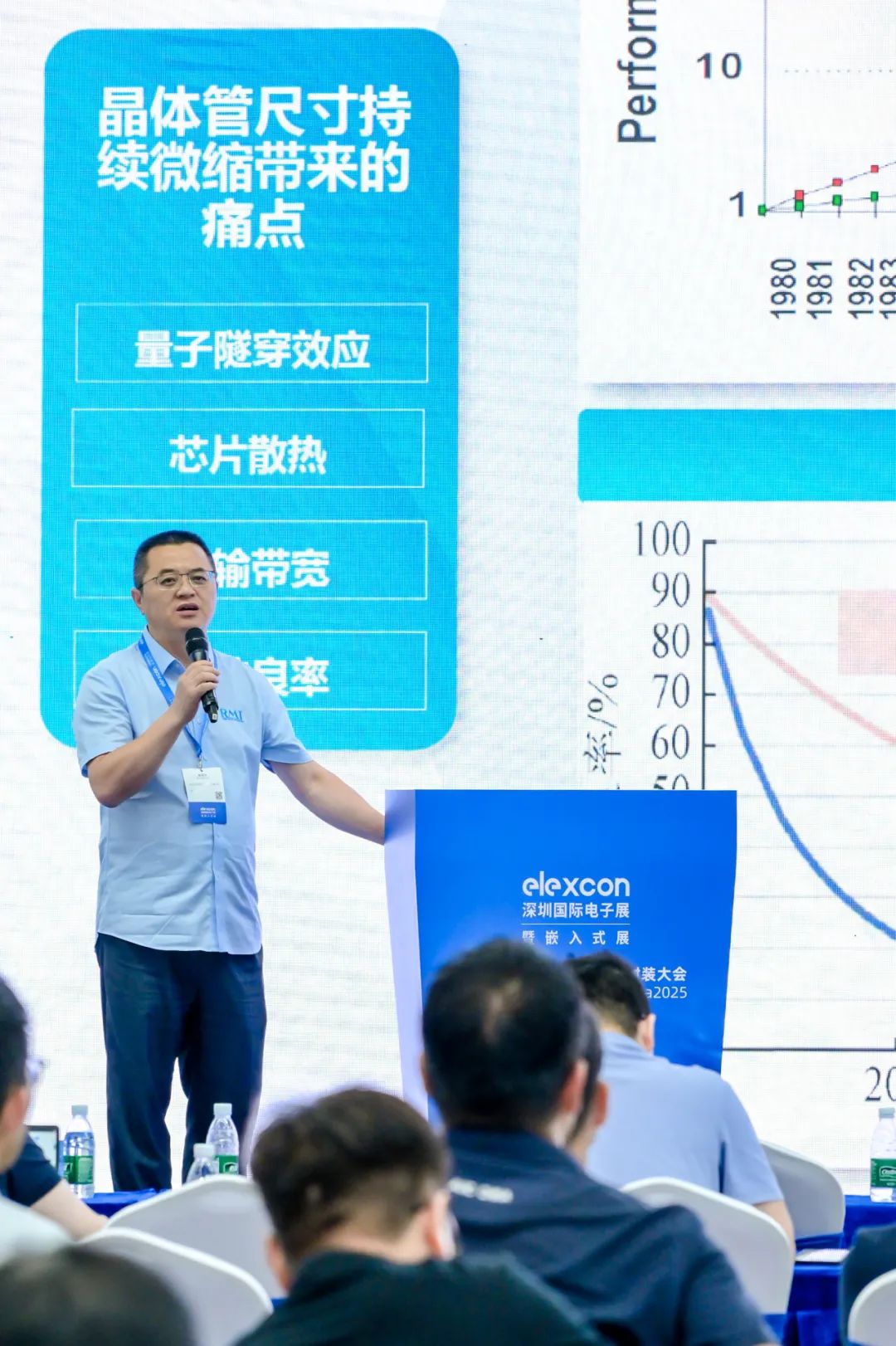

在设计创新与应用落地技术论坛上,集团CMO李卫东先生发表了题为《面向晶上系统的先进封装技术与创新应用》的主题演讲,成为全场瞩目的焦点。他指出,人工智能对算力和带宽需求持续提升,传统算力架构的逐级插损导致带宽衰减、时延激增,低算力密度和能效比,难以满足对更大模型探索和应用场景对空间和能耗的要求。因此,提升节点算力和互联带宽是降低训练和推理成本的关键。晶上系统(Wafer-scale System)凭借晶圆级超异构封装技术,为算力芯片设计带来新的自由度,最大限度集成使能基于内存语义的格点级互联在带宽与时延、能效比、算力密度等关键指标上实现了10倍级性能突破,为算力芯片设计和桌面超算场景应用开辟了全新空间。

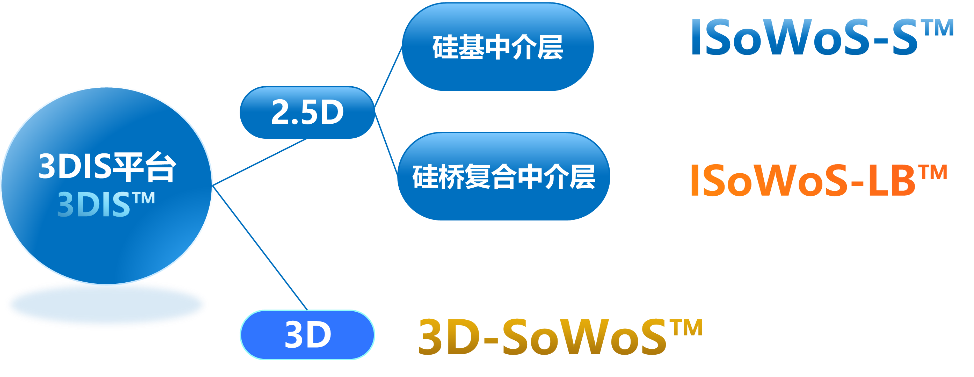

锐杰微科技发布的3DIS™先进封装平台包含三大工艺路径解决方案:

* ISoWoS-S™基于2.5D硅基中介层工艺技术路线,支持2.0X reticle size,bumping size 20um(Min.),pitch size 40um(Min.),4 layer RDL,RDL L/S <1/1um;

* ISoWoS-LB™基于2.5D硅桥复合中介层工艺技术路线,bumping size 20um(Min.),pitch size 40um(Min.),4 layer RDL,RDL L/S <1/1um,桥接转接板厚度60um,TMV尺寸200um;

* 3D-SoWoS™基于logic+mem3D堆叠的工艺技术路线,叠层4层,最大尺寸1.0X reticle size。

▲3DIS™先进封装平台示意图

锐杰微3DIS™先进封装平台的发布,标志着国产先进封装技术已具备从设计仿真、工艺全流程到规模化量产的全栈能力,为AI算力爆发时代提供坚实的底层支撑。

展会现场,锐杰微科技重点展示了基于全流程的先进封装解决方案和多款涵盖3D、2.5D及大颗FCBGA的高端芯片代表性产品,亮点纷呈:“打通3D DPS+AB2工艺节点的智算芯片”、“首款打通RMT全流程,搭载HBM3全国产2.5D AI芯片”、“超大尺寸/大功率/高密度I/O MCM Chiplet超算芯片”、“首款2D光电合封1.6Tbps CPO光引擎芯片”等。同时,公司举办的“扫码送好礼”活动反响热烈,成功吸引了大量专业观众驻足。展台区域人头攒动,汇聚了新老客户、核心供应链伙伴及行业媒体。锐杰微科技的销售、先进封装研究院及市场团队与来访嘉宾就两大全流程Chiplet封装解决方案及潜在项目合作,进行了深入交流与探讨。

在展会备受瞩目的“elexcon创新技术奖”年度评选中,锐杰微科技凭借其在Chiplet领域的卓越贡献,荣膺“Chiplet技术突破贡献奖”。

此次获奖,不仅是对锐杰微科技在Chiplet先进封装领域持续创新与领先实力的高度认可,更是国产Chiplet生态链崛起的重要里程碑。锐杰微科技将继续深耕晶上系统与超异构封装技术,以3DIS™平台为基石,携手产业链伙伴,共同突破算力瓶颈,赋能AI、超算等前沿应用,助力中国集成电路产业迈向更高峰,成为驱动未来算力时代的坚实基石。